今年は忙しくてブログが更新滞り気味┐(´∀`)┌

今年から配属先が変わって、新しい分野に所属することになった。規模の小さい会社だ。今まで設計を外注化していたという事で、道具が殆どそろっておらず、場当たり的な所からのスタートである。こういう会社が存在するから派遣業は潰れない。ありがたいことだ。

1月も終わる頃、とある基板にアルテラのCPLDが搭載された基板があり、外部に設計を委託していたと思ってばかりいたのだが、ふたを開けてみたらどうやら何も手付かずの状態。

委託といっても、中小企業によくある慣れ合いの付き合いでの仕事分担なので、そんなに強くも言えない。かといって、大口客からの受注案件なので、何とかしてあげたい所。

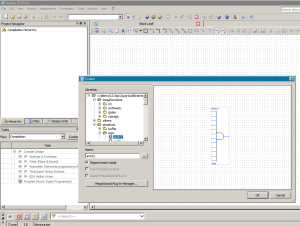

相当昔にMaxPlusIIで設計した事があり、回路図ベースならなんとかなりそうと思い調べたら、今はQuartus II(クォータス)という開発をアルテラから無償でダウンロードできる事を知る。

なぜか、まずそこから調べるのがどうかと思うが(・∀・)

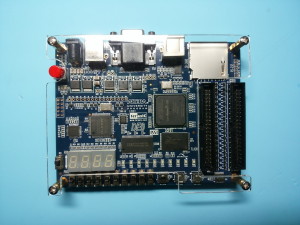

まだ基板ができていないので、なにか評価ボードがないかを調べるとDE0が手軽らしい。といっても、予算も組まれてない案件。ダメもとで以前務めていた設計会社に連絡すると、ありがたいことにDE0を貸して頂けることになった。というわけで、数十年ぶりにCPLDを触ることになる。(正確にはMAX 10KシリーズのFPGAが最後)

評価ボードDE0を動作させてみる。このボードはCycloneIIIなのでQuartusIIのバージョンに注意が必要とのこと。最新は14であるが、DE0を使う場合は13.0をダウンロードする。

何となくVerilog(RTL記述言語)は理解できたが、現場対応には、回路図入力しかない。RTLは課題として、1週間かけてなんとか完成。

シミュレーションは一緒にインストールされるMentor Graphic社のModelSimがあるが、これまた心得がないので、MaxPlusIIについていた古臭い波形エディタを探すも、更に古いバージョン9.0が最後の提供の様だ。幸いプロジェクトファイルは下位互換があったので、9.0でリコンパイルしても通った。

なんとか書き込みファイル(*.pof)が出来上がったと同時に基板がやってきて、USB Blasterで書き込むと、普通に動いてくれた。熟成された会社は、確かにこんな危険な綱渡りをしないだろうが、逆に何もないから何でもできる。何もない状態をどう解決していくかが大事なんだろうな。

デバッグして思ったこと、それはシンボルを書き足したり、配線変更するときに、お絵かきの手間が結構かかる事。テキストベースならC言語と同じ様にちゃちゃっとできるんだろうな。

今度はVerilogで書けるようにしておきたいな(・∀・)

FPGA/CPLD関連はwebを漁れば一杯情報があるので、代表の3つをご紹介。

→Quartus II 9.1 でシミュレーション(しらいむの冒険) 回路図レベルで参考になった

コメントをどうぞ

※メールアドレスとURLの入力は必須ではありません。 入力されたメールアドレスは記事に反映されず、ブログの管理者のみが参照できます。

※投稿には管理者が設定した質問に答える必要があります。